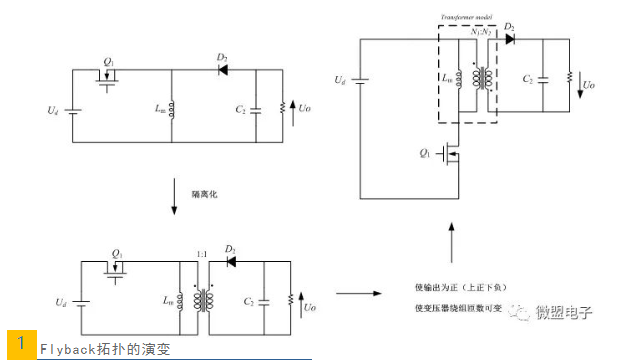

简单回顾一下反激变换的基本原理,Flyback拓扑源于六种基本DC-DC电路之一的Buck-Boost,如下图所示,Buck-boost电路在连续模式(CCM)下的直流增益是-D/(1-D),输出电压极性相反,如果对Buck-Boost进行隔离化,同时使变压器的线圈匝数可变并变换输出极性,就得到了一个Flyback电路。

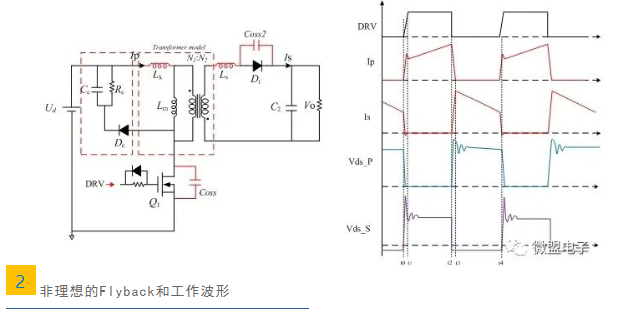

Flyback的工作模式也和大多数开关电源一样,可以工作在连续模式(CCM)、断续模式(DCM)和临界导通模式(BCM)。如下图所示,以工作在连续模式(CCM)的反激为例,可以看到理想的变压器模型中还会存在漏感,实际等效电路中还包括了RCD snubber吸收(增加阻尼,降低Q值),次边的寄生电感Ls与续流二极管串联(包含了杂散电感、副边漏感),以及图中未表示完全的各种寄生的感抗与容抗分布参数。下图给出了驱动信号DRV、原边电流Ip、次边电流Is、原边功率极的漏端电压Vds_P和次边同步整流管的Vds_S(或续流二极管的反向压差)。简单来说,从t0~t2阶段,励磁电感Lm储能;t2~t4阶段,励磁电感储存的能量通过变压器传递到副边给输出电容充电。图中的t2~t3示意性给出了实际工作中存在的换流过程。

为什么要加栅极的驱动缓冲

01

优化EMI性能

EMI包括传导和辐射,前者通过寄生阻抗和其他连接以传导方式耦合到原件,后者通过磁场能量以无线方式传输到待测器件。

回顾下麦克斯韦方程组中的法拉第电磁感应定律:穿过一个曲面的磁通的变化会在此曲面的任意边界路径上产生感应电动势,变化的磁场产生环绕的电场。对于辐射而言,每个环路都是一个小的天线,环路面积的大小、负载电流的大小、测试距离的远近、工作频率的高低、测试方向夹角的差异,都会对辐射产生影响。通过布局的优化、降低di/dt和dv/dt噪声、增加EMI滤波等都可以优化EMI。

02

降低次边续流功率二极管的电压应力

03

从电路设计的角度出发可做哪些优化?

实现这种驱动速度调整的方法有很多,比如可以集成一个简单的逐次逼近的SAR ADC,通过一个时钟沿触发异步时钟,通过SAR逻辑的控制,对驱动MOS的栅极信号从0到Miller平台到来之间的时间差进行量化,通过闭环与目标值进行比较进行调整,直到驱动速度稳定;也可以直接对表征上升沿速度的脉冲信号进行低通滤波获得表征占空比信息的电压信号,对此电压信号进行误差调整。